## B.E. Instrumentation Engineering Fourth Semester IN405 - Digital Circuits

|    | nges :<br>e : T | 2<br>hree H                                                                                                                                                                                                                                                                                                                           | ours * 1 2 4 2 *                                                                                                                                                                  | GUG/W/18/1578<br>Max. Marks: 80 |

|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    | Note            | es: 1<br>2<br>3<br>4<br>5                                                                                                                                                                                                                                                                                                             | <ul><li>All questions carry marks. as indicated.</li><li>Due credit will be given to neatness and adequate dimensions.</li><li>Assume suitable data wherever necessary.</li></ul> |                                 |

| 1. | a)              |                                                                                                                                                                                                                                                                                                                                       | fy the following operations are cumulative but not associative NAND ii) NOR                                                                                                       | 6                               |

|    | b)              | Perfo<br>a)<br>b)<br>c)                                                                                                                                                                                                                                                                                                               | form the following.<br>$(492)_8 = (?)_{16}$ $(1011101)_{Gray} = (?)_{B.}$ $(49)_D - (62)_D \text{ using 2's complement method.}$                                                  | 6                               |

|    | c)              | State                                                                                                                                                                                                                                                                                                                                 | e & prove D' Morgan's Law.  OR                                                                                                                                                    | 4                               |

| 2. | a)              | Desi                                                                                                                                                                                                                                                                                                                                  | gn binary to gray code converter using logic gates.                                                                                                                               | 8                               |

|    | b)              | Realize AND, OR, NOT, Ex-OR Gates using NAND Gates Only.                                                                                                                                                                                                                                                                              |                                                                                                                                                                                   |                                 |

|    | c)              | Write the advantages of 2's compliments over 1's compliments.                                                                                                                                                                                                                                                                         |                                                                                                                                                                                   |                                 |

| 3. | a)              | Draw & explain CMOS circuits for NOR gate.                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                   |                                 |

|    | b)              | For an open-collector TTL gate the specifications are. $V_{OH} = 2.4 V, \ V_{OL} = 0.4 V, \ I_{OH} = 250 \ \mu A$ $I_{OL} = 16 MA, \ I_{IH} = 40 \ \mu A, \ I_{IL} = -1.6 MA$ if 5 such gates are wire - AND ed, and are loaded by similar 6 gates, calculate the value of collector resistor $R_C$ required. Assume $V_{CC} = 5 V$ . |                                                                                                                                                                                   |                                 |

|    |                 |                                                                                                                                                                                                                                                                                                                                       | OR                                                                                                                                                                                |                                 |

| 4. | a)              | i)                                                                                                                                                                                                                                                                                                                                    | re the following terms.  Fan - in  Propagation Delay  ii)  Fan - out  iv)  Noise Margin                                                                                           | 6                               |

|    | b)              | Explain the ECL logic family with neat sketch.                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                   |                                 |

|    | c)              | Com                                                                                                                                                                                                                                                                                                                                   | pare decoder with a Demultiplexer.                                                                                                                                                | 3                               |

5. a) I) Make K - map for the function.  $f = AB + A\overline{C} + C + AD + A\overline{B}C + ABC$

6

- II) Express f in standard SOP form.

- III) Minimize it and realize the minimized expression using NAND gates only.

- b) Design half adder & full adder with logic Ckt and K-map. Explain concept of carry look ahead adder.

OR

**6.** a) Write the difference between

6

10

- i) MUX and DEMUX

- ii) Encoder and Decoder.

- b) Explain octal to binary encoder with suitable truth table.

6

c) Simplify using K - map.

$$F(A,B,C,D) = \pi M (4,6,10,12,13,15)$$

4

8

8

- **7.** a) Differentiate between synchronous and asynchronous counters. Draw & explain 3-bit synchronous counter.

b) Explain the J-K flip flop with logic gate circuit & excitation table.

OR

**8.** a) Convert JK Flip-Flop into T-Flip-Flop.

8

b) Illustrate 3-bit ripple up counter using negative edge triggering.

8

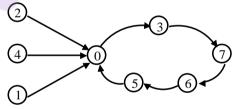

**9.** a) Design a lock free counter for the following states.

8

b) Discuss the function of FPGA with necessary diagram.

8

OR

**10.** a) Design a counter of arbitrary modulo with k-maps.

8

b) Explain VHDL with necessary diagram.

6

c) What is programmable logic Device (PLD)

2

\*\*\*\*\*